If this continues, they’re going to have change the scale from nano to pico. IBM has announced work on a 5 nanometre (5nm) chip in a June 5, 2017 news item on Nanotechnology Now,

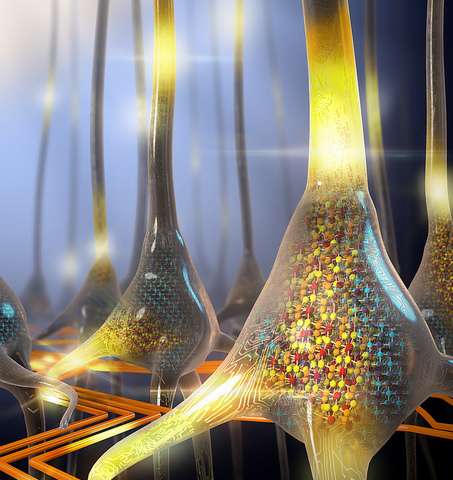

IBM (NYSE: IBM), its Research Alliance partners GLOBALFOUNDRIES and Samsung, and equipment suppliers have developed an industry-first process to build silicon nanosheet transistors that will enable 5 nanometer (nm) chips. The details of the process will be presented at the 2017 Symposia on VLSI Technology and Circuits conference in Kyoto, Japan. In less than two years since developing a 7nm test node chip with 20 billion transistors, scientists have paved the way for 30 billion switches on a fingernail-sized chip.

A June 5, 2017 IBM news release, which originated the news item, spells out some of the details about IBM’s latest breakthrough,

The resulting increase in performance will help accelerate cognitive computing [emphasis mine], the Internet of Things (IoT), and other data-intensive applications delivered in the cloud. The power savings could also mean that the batteries in smartphones and other mobile products could last two to three times longer than today’s devices, before needing to be charged.

Scientists working as part of the IBM-led Research Alliance at the SUNY Polytechnic Institute Colleges of Nanoscale Science and Engineering’s NanoTech Complex in Albany, NY achieved the breakthrough by using stacks of silicon nanosheets as the device structure of the transistor, instead of the standard FinFET architecture, which is the blueprint for the semiconductor industry up through 7nm node technology.

“For business and society to meet the demands of cognitive and cloud computing in the coming years, advancement in semiconductor technology is essential,” said Arvind Krishna, senior vice president, Hybrid Cloud, and director, IBM Research. “That’s why IBM aggressively pursues new and different architectures and materials that push the limits of this industry, and brings them to market in technologies like mainframes and our cognitive systems.”

The silicon nanosheet transistor demonstration, as detailed in the Research Alliance paper Stacked Nanosheet Gate-All-Around Transistor to Enable Scaling Beyond FinFET, and published by VLSI, proves that 5nm chips are possible, more powerful, and not too far off in the future.

Compared to the leading edge 10nm technology available in the market, a nanosheet-based 5nm technology can deliver 40 percent performance enhancement at fixed power, or 75 percent power savings at matched performance. This improvement enables a significant boost to meeting the future demands of artificial intelligence (AI) systems, virtual reality and mobile devices.

Building a New Switch

“This announcement is the latest example of the world-class research that continues to emerge from our groundbreaking public-private partnership in New York,” said Gary Patton, CTO and Head of Worldwide R&D at GLOBALFOUNDRIES. “As we make progress toward commercializing 7nm in 2018 at our Fab 8 manufacturing facility, we are actively pursuing next-generation technologies at 5nm and beyond to maintain technology leadership and enable our customers to produce a smaller, faster, and more cost efficient generation of semiconductors.”

IBM Research has explored nanosheet semiconductor technology for more than 10 years. This work is the first in the industry to demonstrate the feasibility to design and fabricate stacked nanosheet devices with electrical properties superior to FinFET architecture.

This same Extreme Ultraviolet (EUV) lithography approach used to produce the 7nm test node and its 20 billion transistors was applied to the nanosheet transistor architecture. Using EUV lithography, the width of the nanosheets can be adjusted continuously, all within a single manufacturing process or chip design. This adjustability permits the fine-tuning of performance and power for specific circuits – something not possible with today’s FinFET transistor architecture production, which is limited by its current-carrying fin height. Therefore, while FinFET chips can scale to 5nm, simply reducing the amount of space between fins does not provide increased current flow for additional performance.

“Today’s announcement continues the public-private model collaboration with IBM that is energizing SUNY-Polytechnic’s, Albany’s, and New York State’s leadership and innovation in developing next generation technologies,” said Dr. Bahgat Sammakia, Interim President, SUNY Polytechnic Institute. “We believe that enabling the first 5nm transistor is a significant milestone for the entire semiconductor industry as we continue to push beyond the limitations of our current capabilities. SUNY Poly’s partnership with IBM and Empire State Development is a perfect example of how Industry, Government and Academia can successfully collaborate and have a broad and positive impact on society.”

Part of IBM’s $3 billion, five-year investment in chip R&D (announced in 2014), the proof of nanosheet architecture scaling to a 5nm node continues IBM’s legacy of historic contributions to silicon and semiconductor innovation. They include the invention or first implementation of the single cell DRAM, the Dennard Scaling Laws, chemically amplified photoresists, copper interconnect wiring, Silicon on Insulator, strained engineering, multi core microprocessors, immersion lithography, high speed SiGe, High-k gate dielectrics, embedded DRAM, 3D chip stacking and Air gap insulators.

I last wrote about IBM and computer chips in a July 15, 2015 posting regarding their 7nm chip. You may want to scroll down approximately 55% of the way where I note research from MIT (Massachusetts Institute of Technology) about metal nanoparticles with unexpected properties possibly having an impact on nanoelectronics.

Getting back to IBM, they have produced a slick video about their 5nm chip breakthrough,

Meanwhile, Katherine Bourzac provides technical detail in a June 5, 2017 posting on the Nanoclast blog (on the IEEE [Institute of Electrical and Electronics Engineers] website), Note: A link has been removed,

Researchers at IBM believe the future of the transistor is in stacked nanosheets. …

Today’s state-of-the-art transistor is the finFET, named for the fin-like ridges of current-carrying silicon that project from the chip’s surface. The silicon fins are surrounded on their three exposed sides by a structure called the gate. The gate switches the flow of current on, and prevents electrons from leaking out when the transistor is off. This design is expected to last from this year’s bleeding-edge process technology, the “10-nanometer” node, through the next node, 7 nanometers. But any smaller, and these transistors will become difficult to switch off: electrons will leak out, even with the three-sided gates.

So the semiconductor industry has been working on alternatives for the upcoming 5 nanometer node. One popular idea is to use lateral silicon nanowires that are completely surrounded by the gate, preventing electron leaks and saving power. This design is called “gate all around.” IBM’s new design is a variation on this. In their test chips, each transistor is made up of three stacked horizontal sheets of silicon, each only a few nanometers thick and completely surrounded by a gate.

Why a sheet instead of a wire? Huiming Bu, director of silicon integration and devices at IBM, says nanosheets can bring back one of the benefits of pre-finFET, planar designs. Designers used to be able to vary the width of a transistor to prioritize fast operations or energy efficiency. Varying the amount of silicon in a finFET transistor is not practicable because it would mean making some fins taller and other shorter. Fins must all be the same height due to manufacturing constraints, says Bu.

IBM’s nanosheets can range from 8 to 50 nanometers in width. “Wider gives you better performance but takes more power, smaller width relaxes performance but reduces power use,” says Bu. This will allow circuit designers to pick and choose what they need, whether they are making a power efficient mobile chip processor or designing a bank of SRAM memory. “We are bringing flexibility back to the designers,” he says.

The test chips have 30 billion transistors. …

It was a struggle trying to edit Bourzac’s posting with its good detail and clear writing. I encourage you to read it (June 5, 2017 posting) in its entirety.

As for where this drive downwards to the ‘ever smaller’ is going, there’s Dexter’s Johnson’s June 29, 2017 posting about another IBM team’s research on his Nanoclast blog on the IEEE website (Note: Links have been removed),

There have been increasing signs coming from the research community that carbon nanotubes are beginning to step up to the challenge of offering a real alternative to silicon-based complementary metal-oxide semiconductor (CMOS) transistors.

Now, researchers at IBM Thomas J. Watson Research Center have advanced carbon nanotube-based transistors another step toward meeting the demands of the International Technology Roadmap for Semiconductors (ITRS) for the next decade. The IBM researchers have fabricated a p-channel transistor based on carbon nanotubes that takes up less than half the space of leading silicon technologies while operating at a lower voltage.

In research described in the journal Science, the IBM scientists used a carbon nanotube p-channel to reduce the transistor footprint; their transistor contains all components to 40 square nanometers [emphasis mine], an ITRS roadmap benchmark for ten years out.

One of the keys to being able to reduce the transistor to such a small size is the use of the carbon nanotube as the channel in place of silicon. The nanotube is only 1 nanometer thick. Such thinness offers a significant advantage in electrostatics, so that it’s possible to reduce the device gate length to 10 nanometers without seeing the device performance adversely affected by short-channel effects. An additional benefit of the nanotubes is that the electrons travel much faster, which contributes to a higher level of device performance.

Happy reading!