This research into an analogue memristor comes from The Korea Institute of Science and Technology (KIST) according to a September 20, 2022 news item on Nanowerk, Note: A link has been removed,

Neuromorphic computing system technology mimicking the human brain has emerged and overcome the limitation of excessive power consumption regarding the existing von Neumann computing method. A high-performance, analog artificial synapse device, capable of expressing various synapse connection strengths, is required to implement a semiconductor device that uses a brain information transmission method. This method uses signals transmitted between neurons when a neuron generates a spike signal.

However, considering conventional resistance-variable memory devices widely used as artificial synapses, as the filament grows with varying resistance, the electric field increases, causing a feedback phenomenon, resulting in rapid filament growth. Therefore, it is challenging to implement considerable plasticity while maintaining analog (gradual) resistance variation concerning the filament type.

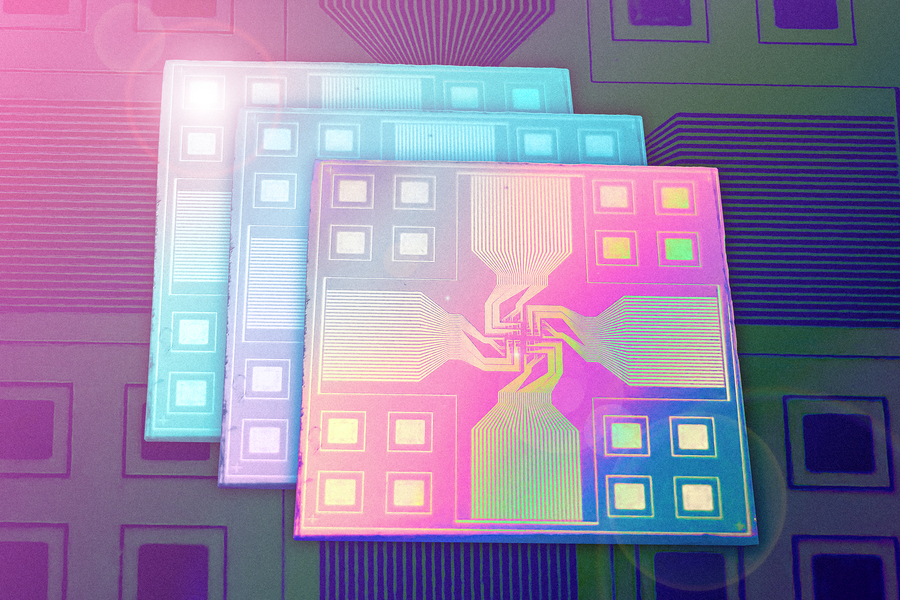

The Korea Institute of Science and Technology (KIST), led by Dr. YeonJoo Jeong’s team at the Center for Neuromorphic Engineering, solved the limitations of analog synaptic characteristics, plasticity and information preservation, which are chronic obstacles regarding memristors, neuromorphic semiconductor devices. He announced the development of an artificial synaptic semiconductor device capable of highly reliable neuromorphic computing (Nature Communications, “Cluster-type analogue memristor by engineering redox dynamics for high-performance neuromorphic computing”).

…

A September 20, 2022 (Korea) National Research Council of Science & Technology press release on EurekAlert, which originated the news item, delves further into the research,

The KIST research team fine-tuned the redox properties of active electrode ions to solve small synaptic plasticity hindering the performance of existing neuromorphic semiconductor devices. Furthermore, various transition metals were doped and used in the synaptic device, controlling the reduction probability of active electrode ions. It was discovered that the high reduction probability of ions is a critical variable in the development of high-performance artificial synaptic devices.

Therefore, a titanium transition metal, having a high ion reduction probability, was introduced by the research team into an existing artificial synaptic device. This maintains the synapse’s analog characteristics and the device plasticity at the synapse of the biological brain, approximately five times the difference between high and low resistances. Furthermore, they developed a high-performance neuromorphic semiconductor that is approximately 50 times more efficient.

Additionally, due to the high alloy formation reaction concerning the doped titanium transition metal, the information retention increased up to 63 times compared with the existing artificial synaptic device. Furthermore, brain functions, including long-term potentiation and long-term depression, could be more precisely simulated.

The team implemented an artificial neural network learning pattern using the developed artificial synaptic device and attempted artificial intelligence image recognition learning. As a result, the error rate was reduced by more than 60% compared with the existing artificial synaptic device; additionally, the handwriting image pattern (MNIST) recognition accuracy increased by more than 69%. The research team confirmed the feasibility of a high-performance neuromorphic computing system through this improved the artificial synaptic device.

Dr. Jeong of KIST stated, “This study drastically improved the synaptic range of motion and information preservation, which were the greatest technical barriers of existing synaptic mimics.” “In the developed artificial synapse device, the device’s analog operation area to express the synapse’s various connection strengths has been maximized, so the performance of brain simulation-based artificial intelligence computing will be improved.” Additionally, he mentioned, “In the follow-up research, we will manufacture a neuromorphic semiconductor chip based on the developed artificial synapse device to realize a high-performance artificial intelligence system, thereby further enhancing competitiveness in the domestic system and artificial intelligence semiconductor field.”

Here’s a link to and a citation for the paper,

Cluster-type analogue memristor by engineering redox dynamics for high-performance neuromorphic computing by Jaehyun Kang, Taeyoon Kim, Suman Hu, Jaewook Kim, Joon Young Kwak, Jongkil Park, Jong Keuk Park, Inho Kim, Suyoun Lee, Sangbum Kim & YeonJoo Jeong. Nature Communications volume 13, Article number: 4040 (2022) DOI: https://doi.org/10.1038/s41467-022-31804-4 Published: 12 July 2022

This paper is open access.